文章编号:1002-2082(2007)01-0007-05

# 基于Nios II的非制冷红外图像处理系统研究

孙恋君, 张俊举, 谌 巧, 常本康, 钱芸生

(南京理工大学 电子工程与光电技术学院, 南京 210094)

**摘要:** 设计一个非制冷红外图像处理系统,该系统放弃了目前普遍应用的数字信号处理器(DSP)+现场可编程门阵列(FPGA)的系统构架,采用基于FPGA的Nios II嵌入式处理器的系统构架,实现了系统的小型化。提出一种基于流水线结构的信号处理方法,并利用Nios II嵌入式处理器软硬件开发工具,实现了在该系统上对非制冷红外焦平面阵列非均匀性进行校正和盲元补偿的实时处理,降低了系统的工作频率。实验结果表明:该系统能够对非制冷红外图像进行实时处理,工作性能稳定,处理效果良好。

**关键词:** 非制冷红外焦平面阵列;图像处理;嵌入式处理器;现场可编程门阵列;Nios II

中图分类号:TN215

文献标志码:A

## Study of uncooled infrared image processing system based on Nios II

SUN Lian-jun, ZHANG Jun-ju, CHEN Qiao, CHANG Ben-kang, QIAN Yun-sheng

(School of Electronic Engineering & Optoelectronic Techniques,

Nanjing University of Science and Technology, Nanjing 210094, China)

**Abstract:** A miniaturized uncooled infrared image processing system is designed by adopting the structure of Field Programmable Gate Array (FPGA) embedded with Nios II processor instead of Digital Signal Processor (DSP) + FPGA structure. A signal processing method based on pipelining model is proposed and applied in the system with the hardware and software development tools of Nios II embedded processor. As indicated by the experiment result, the system can process the uncooled infrared image in real time. It has the merits of good performance and small volume.

**Key words:** IRFPA; image processing; embedded processor; FPGA; Nios II

## 引言

非制冷红外焦平面阵列(IRFPA)探测器凭借其价格低、体积小、功耗低、性能可靠、操作方便等诸多优势,在军事和民用领域有越来越广泛的应用前景,成为当今世界高技术领域发展的热点之一。众所周知,非制冷红外焦平面阵列的固有非均匀性和盲元使其需要依靠外部图像处理系统才能对原始红外图像进行校正和增强<sup>[1]</sup>等,从而获得较好的成像质量。最初的红外图像处理系统采用基于DSP构架的电路<sup>[2]</sup>,虽然可以满足处理过程中大量数据

计算的要求,但是,因为系统的可编程能力较差而增加了系统软硬件设计开发的复杂性。目前,红外图像处理系统大多采用基于DSP+FPGA架构的电路<sup>[3]</sup>。其中,DSP凭借其强大的运算能力主要实现数据运算、数据通信和系统管理等功能;FPGA依靠其灵活的在线可编程能力主要实现信号处理、视频合成和时序管理等功能;二者相互配合,完成对红外图像的实时处理。然而,在这些系统中,基于总线分时复用的DSP和FPGA需要频繁转换对系统的控制权,这必然会降低整个系统的数据传输效

率,增加系统时钟控制逻辑的复杂度,给系统的设计和应用带来诸多不便。更重要的是,采用 DSP+FPGA 架构的电路,需要在 DSP 和 FPGA 之间添加许多隔离器件,因而导致系统体积偏大,难以适应很多应用领域对系统小型化的要求。

随着 FPGA 技术的发展,其功能也日益强大。为了使红外图像处理系统更加小型化,以适用对体积、功耗等具有特殊要求的应用场所,利用 SOPC 设计方法,在单片高性能的FPGA 器件上形成的图像处理系统拥有巨大的发展潜力。因此,本文设计了一种基于美国 Altera 公司开发的 Nios II 嵌入式处理器的非制冷红外图像处理系统,同时提出一种基于流水线结构的信号处理方法,并利用Nios II 嵌入式处理器的软硬件开发工具在该系统上成功实现了对非制冷红外焦平面阵列非均匀性进行校正和盲元补偿的实时处理。通过对实验中系统形成的原始图像和校正图像进行比较,可以明显看出该系统工作性能稳定,处理效果良好,体积小,便于携带,完全能够满足实际应用需要。

## 1 系统结构及工作原理

### 1.1 系统结构

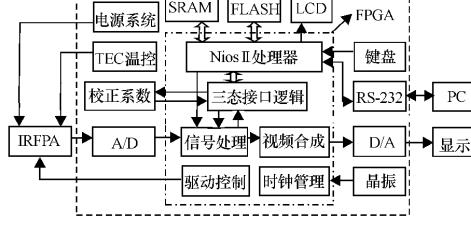

基于 Nios II 嵌入式处理器的非制冷红外图像处理系统结构如图1 所示。该系统主要由FPGA 芯片、A/D 转换器、D/A 转换器、数据/程序存储器、TEC 温控电路,串行通信接口、LCD 显示屏、键盘和电源系统等组成,可实现对 IRFPA 所成图像信号的采集、处理、合成以及相应的数据通信和程序控制等功能。

图 1 基于 Nios II 的非制冷红外图像处理系统结构

Fig. 1 Block diagram of uncooled infrared image processing system based on Nios II

系统中FPGA 处于核心位置,主要由Nios II 处理器和外部逻辑组成,内嵌的Nios II 处理器主要完成系统管理、数据通信、数据加载、LCD 字符界面控制等功能;外部逻辑承担信号处理、视频合成、时

序管理等功能,并且为 IRFPA 提供数字驱动信号,也为 A/D、D/A 和 IRFPA 提供时钟信号。数据/程序存储器包括 FLASH、SDRAM 和 SRAM,用于系统工作过程中应用程序、图像数据及校正系数的存储。TEC 温控电路对 IRFPA 进行自适应温度控制,串行通信接口进行系统与外部 PC 间的数据通信,LCD 显示屏和键盘提供系统的控制界面,电源系统为系统和 IRFPA 提供电源。

### 1.2 系统工作原理

系统开机或复位后,TEC 温控电路立即开始调节 IRFPA 的温度向设定温度靠拢,直到温度稳定(温度稳定精度为 4 mK);与此同时,FPGA 从 FLASH 中加载程序并完成系统的初始化和片外设备的自检;系统初始化完成后,IRFPA 在温度完全稳定后接收 FPGA 发出的驱动控制信号开始正常工作,其输出的图像信号经过 A/D 转换后,送入 FPGA 进行处理。

正常工作情况下,系统有 2 种工作模式:标定模式和校正模式。整个系统的工作状态通过外部键盘选择控制,工作模式通过 LCD 显示出来。在标定模式下,根据两点非均匀性校正算法,Nios II 处理器控制系统对外置标准黑体面源在高、低 2 个温度下的图像数据进行传输,输入 SRAM 中暂存,在成功获取 2 帧标定图像数据后,Nios II 处理器接收中断请求,运行相应的校正系数计算程序,分别获得 IRFPA 每个像素的增益校正因子  $G_{i,j}$  和偏移量校正因子  $O_{i,j}$ ,同时计算出盲元标志位,形成带盲元标志的校正系数存入 Flash 中,完成校正系数的获取或更新后程序跳出中断,并轮询键盘状态以确定进一步操作;与此同时,FPGA 不进行任何信号处理,直接把未经校正的原始图像信号送往视频合成模块,并通过监视器显示出来。在校正模式下,Nios II 处理器将存储在 Flash 中带盲元标志的增益校正系数和偏移校正系数分别转移到外部 2 片存储校正系数的 SRAM 中,形成一个校正系数查找表(LUT);Nios II 处理器将这 2 片 SRAM 的控制权交给外部信号处理模块,对原始图像信号进行两点非均匀性校正和盲元补偿;校正后的图像数据经过视频合成和 D/A 转换,最终显示出来。

## 2 基于FPGA 的 Nios II 嵌入式处理器

### 2.1 Nios II 处理器简介

Nios II 处理器是美国 Altera 公司开发的一种

基于FPGA、可配置的、单指令流的32 位RISC 软核

嵌入式处理器<sup>[4]</sup>。处理器大部分指令可以在1个时钟周期内完成,工作频率达百兆级,可以获得超过200 DMIPS 的性能,还可结合用户定制指令和自定义逻辑构成一个基于FPGA 的片上系统。

Nios II 处理器系列包括3 种CPU 内核,即注重性能的快速型(Nios II /f),注重尺寸的经济型(Nios II /e)和兼顾性能和尺寸的标准型(Nios II /s)。处理器配备超过60 种IP 内核供用户创建一组适合于自己应用的外设、存储器和I/O 接口;支持无限DMA 数据传输方式,提供可配置的硬件及软件调试特性;最多允许用户定制256 个用户指令,并且可以构建多CPU 内核系统。

Nios II 处理器采用Avalon 交换式总线技术。通过Avalon 交换矩阵在处理器、外围设备和接口电路之间实现网络连接,规范定义了主从端口之间数据传输的信号和时序,并支持数据总线的复用、地址译码、等待周期的产生、外设的地址对齐、中断优先级的指定以及高级的交换式总线传输。Avalon 总线由SOPC Builder 自动生成,可以根据设计过程中系统组件的需要随时增删更新。

Nios II 处理器拥有灵活的可编程能力,以及单芯片的系统处理方案和日益强大的处理能力,可大大简化系统设计的复杂性,降低系统的开发成本,增强系统运行的可靠性。

## 2.2 Nios II 处理器系统开发流程

开发Nios II 处理器系统需要以下软硬件开发工具:Windos NT/2000/XP 操作系统、Quartus II 4.0 或更高版本、SOPC Builder 软件、Nios II IDE 集成开发环境<sup>[5]</sup>以及相应的硬件电路板。

Nios II 处理器系统的硬件设计过程如下:1)用SOPC Builder 系统综合软件选取合适的CPU、存储器及外设,并定制它们的功能,生成一个Nios II 处理器系统;2)用Quartus II 软件进行FPGA 器件选取,处理器外部逻辑编写,系统I/O 管脚分配和布局布线,最后在一定的硬件编译选项和时序约束下进行编译,生成配置文件;3)用Quartus II 编程器和 Alter 下载电缆,将配置文件下载到相应硬件电路板上。

Nios II 处理器系统的软件设计过程如下:1)在Nios II IDE 中编写C/C++ 应用程序软件;2)在Nios II IDE 中对编写的软件工程进行编译和在线调试;3)将最终的应用程序软件下载到硬件电路板上并运行。

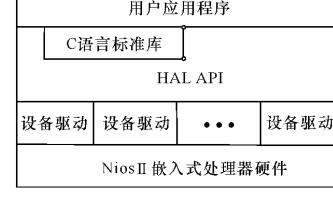

IDE 基于用户在SOPC Builder 中创建的Nios II 处理器系统会自动生成一个HAL(hardware abstraction layer,硬件抽象层)系统库。HAL 库所基于的系统层次图如图2 所示。它为设计可提供与ANSI C 合成的标准库、设备驱动、HAL 应用程序接口(API)、系统初始化和设备初始化等支持。

图2 HAL 系统库层次图

Fig. 2 Diagram of HAL

HAL 库为嵌入式系统中常见的外围设备提供了通用的设备模型,可以让用户无需考虑底层硬件就能利用与之相一致的API 编写应用程序。同时通过HAL 库本身集成的ANSI C 标准库,也可以用C 语言中的一些库函数来实现外设的访问。

## 3 系统设计

本文设计的基于Nios II 非制冷红外图像处理系统,考虑了信号处理对工作频率和资源的要求。其中FPGA 器件选择Cyclone 系列EP1C20F400C8 芯片,配置器件为EPCS4, Nios II CPU 选择标准型(Nios II /s)。

### 3.1 Nios II 处理器系统设计

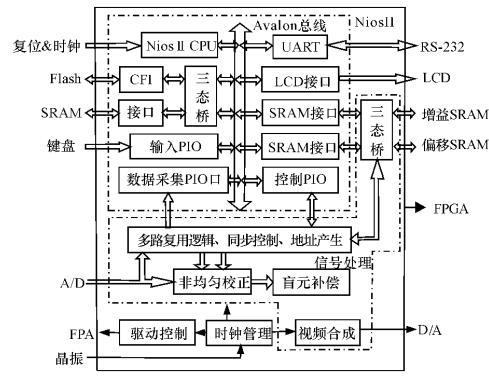

整个图像处理系统以FPGA 为核心,在FPGA 内部设计一个Nios II 嵌入式处理器系统,其原理如图3 所示。按功能可划分为Nios II 处理器、信号处理模块、驱动控制逻辑和时钟管理逻辑。

图3 中, Nios II 处理器是整个系统的控制核心,主要实现视频信号采集、传输、LCD 字符界面显示控制,校正参数的提取以及校正参数的存储和更新控制等功能,同时通过PIO 口对处理电路的工作模式进行控制。

信号处理模块是系统信号处理的核心,主要功能是进行非均匀校正、盲元补偿,校正完的图像通过视频合成模块处理后,送到后端D/A,最后显示出来。此外,在信号处理模块中还有多路复用逻辑模块以及三态桥等。多路复用逻辑和同步控制主要用于在校正模式下控制片外存储校正系数的SRAM,同时,通过三态桥,在Nios II 处理器的控制

用户在Nios II IDE 中创建一个新的工程时,

下,信号处理模块与 Nios II 处理器对 SRAM 进行分时复用。

图 3 FPGA 内部设计原理

Fig. 3 Internal design principle of FPGA

另外,驱动控制逻辑可为 IRFPA 提供驱动信号,时钟管理逻辑为 A/D、D/A 及红外焦平面阵列等提供时钟信号。

### 3.2 流水线结构信号处理方法

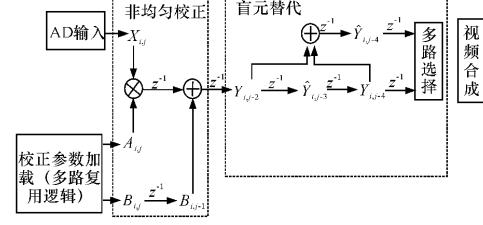

上述信号处理模块采用一种实时信号处理同步时序电路结构,称为流水线结构,如图 4 所示。

图 4 信号处理模块流程图

Fig. 4 Flow chat of signal processing module

系统处于校正模式时,图像数据逐个像素地从 A/D 输入,其传输速度和 IRFPA 的主时钟相同。此时,系数加载模块在 IRFPA 提供的同步信号 DATAVALID 和 LINE1 的作用下,产生对应像素的地址信号,读取该像素的校正系数和盲元标志。根据系统要求,校正系数和盲元标志从高位到低位依次存储在同一个双字(32 位)内,其中增益校正系数  $G_{i,j}$  占 1 个字(16 位),偏移校正系数  $O_{i,j}$  占 15 位,而盲元标志  $F_{i,j}$  占 1 位。

图像数据和校正系数、盲元标志同时进入信号处理流水线。首先进行增益校正,此时增益校正因子  $G_{i,j}$  和 15 位偏移量校正因子  $O_{i,j}$  都保存在 D 触发

器内。经过增益校正后的图像数据经一级流水后进行偏移校正,偏移校正系数  $O_{i,j}$  也经过了一级流水后同时到达偏移校正。经过增益和偏移校正以后,图像数据将进行盲元补偿。此时,加法器一直计算 1 个像素前后 2 个像素的平均值,该平均值作为预备的替代值与该像素同时向后传递,一直到双路选通开关。盲元标志自从进入流水线后就一级一级地向后传递,一直到双路选通开关级。在选通开关处,盲元标志将决定是平均值向后输出还是真实值向后输出,从而实现盲元的补偿。

由以上分析可以看出,采用流水线结构实时信号处理方法,不仅简化了处理流程,降低了系统工作频率,使得系统运行更加平稳,而且缩小了数据存储空间,减少了延迟时间。

### 3.3 Nios II 处理器软件设计

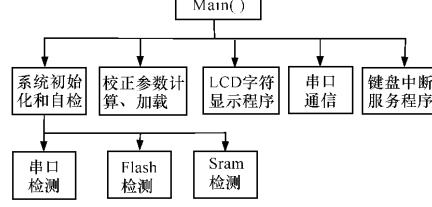

根据整个系统工作需要, Nios II 处理器软件程序结构如图 5 所示。

图 5 Nios II 处理器软件程序结构图

Fig. 5 Program structure of Nios II processor software

主程序开始运行后,首先对系统外围设备进行检测。自检程序包括对串口、FLASH 及 SRAM 等的检测。检测结果通过 LCD 显示出来。校正系数的计算、加载和串口通信等都是通过中断方式实现的。外围设备的检测完成后,如果系统正常,程序进入键盘中断服务程序。键盘服务程序主要实现对系统的控制,可根据键盘的状态进入不同的中断程序来实现处理器工作模式的转换。

### 3.4 实验结果

采用上述软硬件设计和信号处理方法的非制冷红外图像处理器系统,连接上 320×240 微测辐射热计 IRFPA 探测器和监视器,通电后可以开始工作。图 6 为系统联调实验过程中采集的 2 幅红外图像,目标为人脸和手。其中图 6(a)是未经过任何处理的原始图像,可以看到目标几乎完全被 IRFPA 固定图案噪声所掩盖,并且盲元对图像质量影响比较明显;图 6(b)是经过两点非均匀性校正和盲元补偿后的图像,可以看到目标成像比较清

晰,并且没有盲元的干扰,图像不仅对比度较好,而且很多图像细节,例如人的头发、眉毛、鼻子和手关节等也显现出来了。对比这 2 幅图像可知,该系统完全能够达到设计目的,满足设计要求。

(a) 原始图像

(b) 处理后图像

图 6 非制冷红外图像处理前后对比

Fig. 6 Comparison of original image with processed image

## 4 结论

我们利用 Nios II 嵌入式处理器,基于流水线结构的图像信号处理方法,采用基于 FPGA 的系统构架,设计出一种新型非制冷红外图像处理系统。与原有的基于 DSP 构架或基于 DSP+FPGA 构架的系统相比,真正意义上实现了 SOPC。通过对该系统进行联调实验,证明该系统能够稳定且有效地对非制冷红外图像进行非均匀性校正和盲元替代处理,并且与现有的红外图像处理系统相比,体积更

小,更便携,也更适合于实际应用的需要。随着 Nios II CPU 频率的不断提高,处理器功能的不断增强和红外图像处理算法的不断改进,系统的设计也在不断地优化,功能也会不断地完善,其应用范围也将会不断地扩大。

### 参考文献:

- [1] 邱慧,于起峰,张小虎. 一种基于灰度变换的红外图像增强算法[J]. 应用光学,2006,27(1):12-14.

DI Hui, YU Qi-feng, ZHANG Xiao-hu. An algorithm for infrared image enhancement based on gray scale transform [J]. Journal of Applied Optics, 2006, 27 (1):12-14. (in Chinese)

- [2] 邢素霞,常本康,钱芸生,等. 基于高速DSP的红外图像处理电路研究[J]. 红外与激光工程,2004, 33 (3):292-295.

XING Su-xia, CHANG Ben-kang, QIAN Yun-sheng, et al. Study on infrared image processing circuit based on high speed DSP [J]. Infrared and Laser Engineering, 2004, 33 (3): 292-295. (in Chinese)

- [3] 赵广州,张天序,王新赛,等. 基于 DSP 和 FPGA 的模块化实时图像处理系统设计[J]. 华中科技大学学报:自然科学版,2002, 32(10):4-6.

ZHAO Guang-zhou, ZHANG Tian-xu, WANG Xin-sai, et al. Modularized real-time image processing system based on DSP and FPGA [J]. Huazhong University of Science and Technology : Nature Science Edition, 2002, 32(10):4-6. (in Chinese)

- [4] Altera. Nios II Processor Reference Handbook[EB/OL]. [2005-03-01]. <http://www.altera.com>.

- [5] Altera. Nios II Software Developer's Handbook[EB/OL]. [2005-03-01]. <http://www.altera.com>.